# Power modules for E-vehicles — available solutions and future challenges

Marcus Lipppert – Key Account Manager at Starpower Europe

## Key design objectives for Power Modules

- 1. Increase Power Density per package

- Chip technology → lower V<sub>CFsat</sub>

- Contacting technology within the power module → lower R<sub>thJC</sub>, higher T<sub>iop</sub>

$$I_{c} = \frac{\sqrt{R_{thJC} \cdot VT0^{-2} + 4 \cdot RCE \cdot \left(T_{j(max)} - T_{c}\right)}}{2 \cdot \sqrt{R_{thJC} \cdot RCE}} - \frac{VT0}{2 \cdot RCE}$$

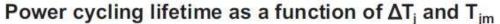

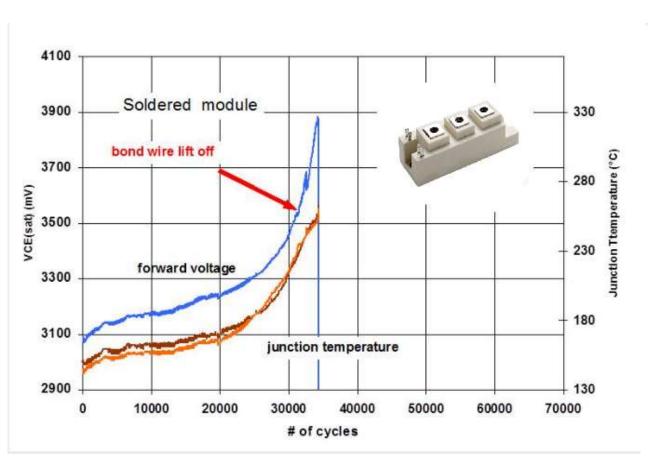

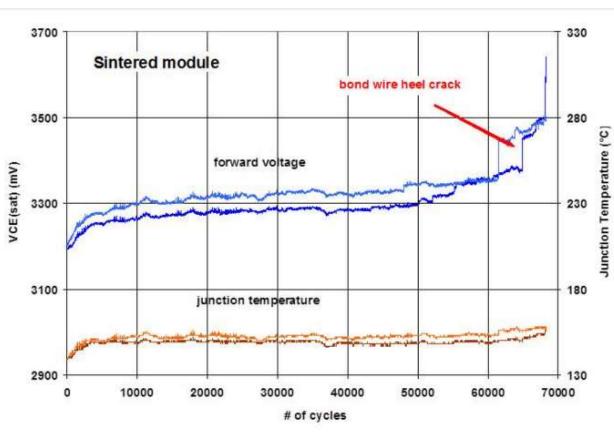

- 2. Increase reliability → number of power cycles

- Number of power cycles will decrease with increasing T<sub>ion</sub>

- Cost optimization

#### Lifetime Industrial Standard

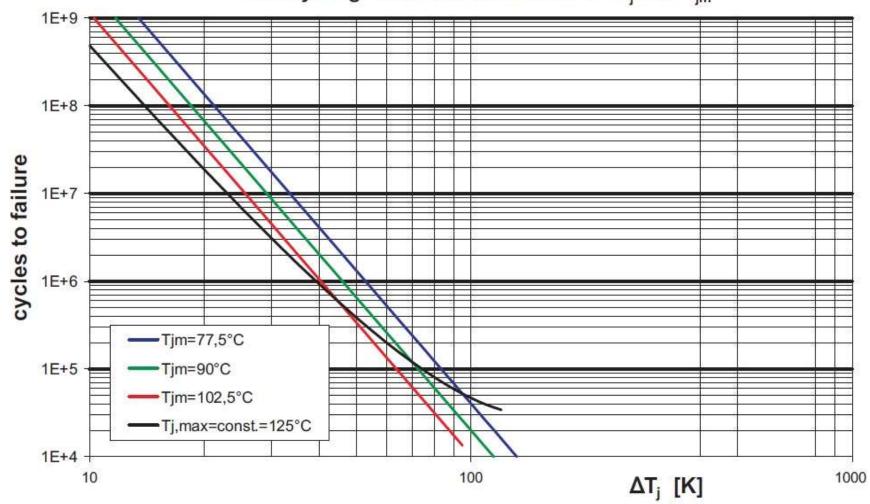

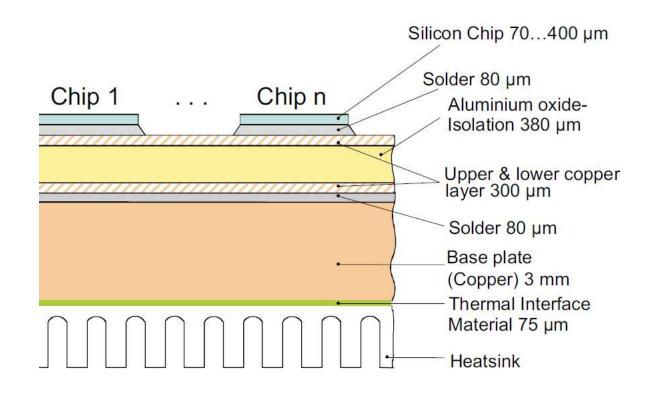

#### Thermal losses for standard modules

Source: Semikron Application Handbook

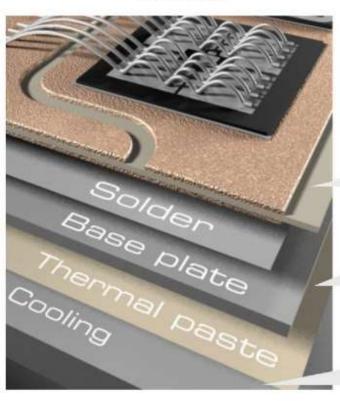

### Pre-applied TIM

Modules with Baseplate

Modules without Baseplate

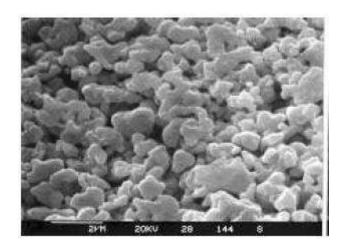

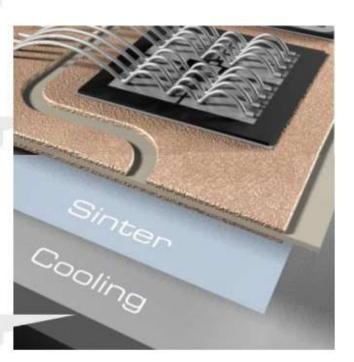

# Sintering instead of Soldering

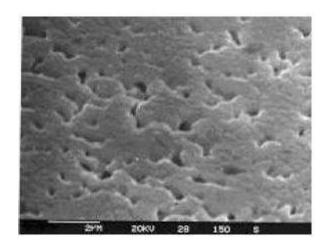

Ag nano particles

Sintering press

Temperature & Pressure

Density of sintered layer very close to density of Ag

- Fine grained Ag particles sintered at 250°C

- Achieving a very stable connection chip-DBC up to Ag melting point of 962°C

- 4 x increased melting temperature of Ag compared with standard solder results in 3 x higher power cycling capability

## Sintering instead of Soldering

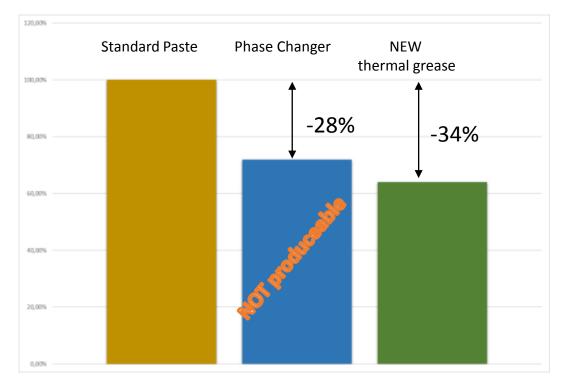

#### **PINFIN**

- Sintering DBC with sintered chips straight to the heatsink will allow a design without baseplate and TIM

- Achievable reduction in R<sub>thi-a</sub> of about 25%

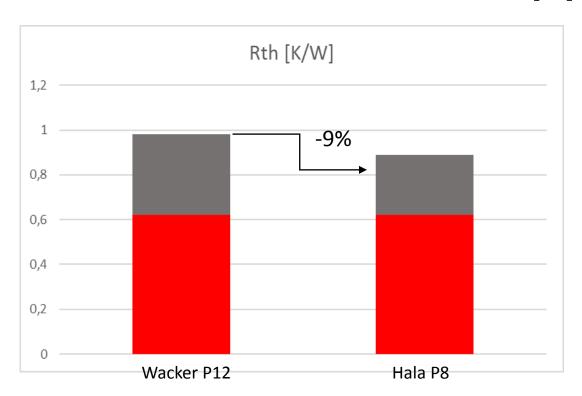

Standard Technology

$R_{th[j-a]}[K/W]$ 0.85 0.61

Chip + DCB 0.25 0.24

Thermal paste 0.25

Cooling 0.35 0.37 Sintern & PINFIN Technology

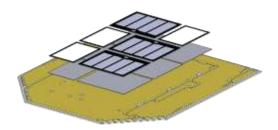

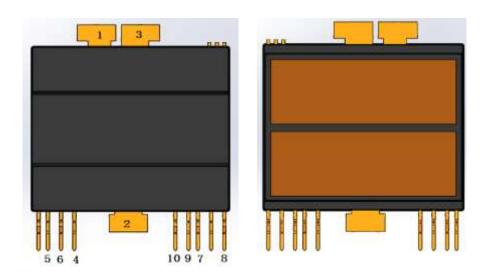

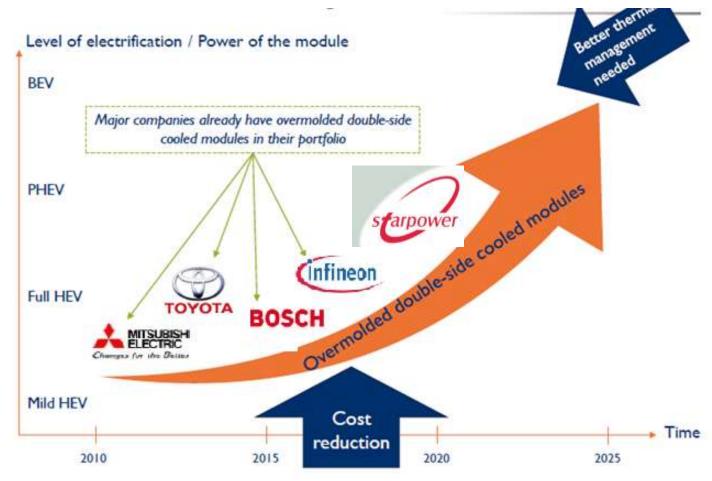

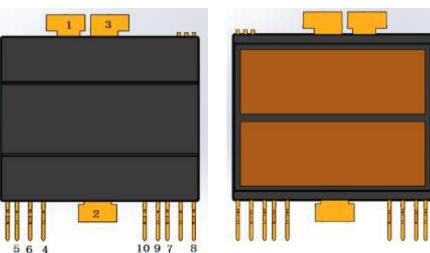

## Single & Double Side Cooled Modules

- Highest power density per module size in order to facilitate space and performance requirements for EVapplications

- Better thermal management due to double side cooling

### Single & Double Side Cooled Modules

- Smallest package size / A

- → Low cost

- Heat can be dissipated in two directions

- → Efficient heat dissipation

- → High power density

- Small package height, DC+/- close together, no bond wires

- → Low parasitic inductance

- Massive copper terminals around the dies

- → Low losses

- → Large thermal capability

- → Low Tj fluctuation

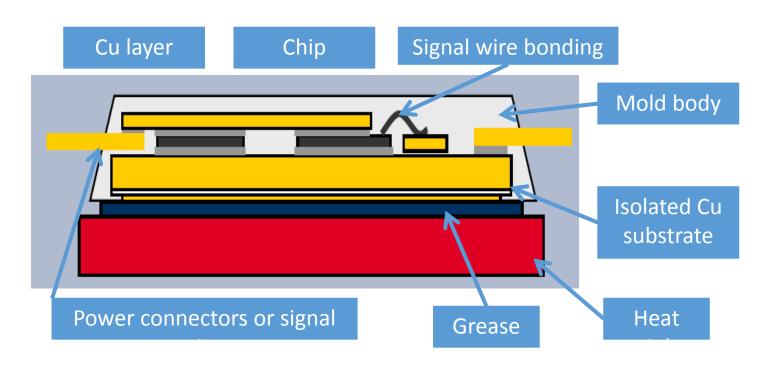

# Core Technologies: Current Density by Design

#### Reduced power dissipation:

- Low ohmic module design and IGBT-contacting

- Low inductive module design

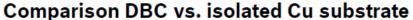

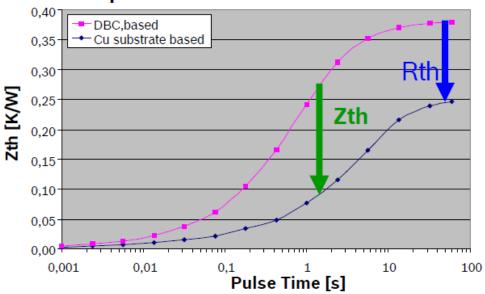

#### Improved heat flow to heat sink:

- Up to 70% improvement in Zth

- Up to 30% improvement in Rth

#### Due to

- double sided IGBT cooling by solder contacting

- optimized heat spreading by thick Cu layer

#### Common Packages

14 juni 2018 1931 Congrescentrum Den Bosch