tijdschrift van het

nederlands elektronicaen radiogenootschap

- 1978

nederlands elektronicaen radiogenootschap Nederlands Elektronica- en Radiogenootschap Postbus 39, Leidschendam. Gironummer 94746 t.n.v. Penningmeester NERG, Leidschendam.

### HET GENOOTSCHAP

Het Genootschap stelt zich ten doel in Nederland en de Overzeese Rijksdelen de wetenschappelijke ontwikkeling en de toepassing van de elektronica en de radio in de ruimste zin te bevorderen.

### Bestuur

Dr. Ir. W.Herstel, voorzitter

Prof.ir. E. Goldbohm, vice-voorzitter

Ir. G.A.v.d.Spek, secretaris

Ir. E. Goldstern, penningmeester

Ing. J.W.A.v.d.Scheer, programma commissaris

Ir. J.H. Huijsing

Dr.Ir. J.B.H.Peek

Prof.ir. C. Rodenburg

Prof.dr.ir. J.P.M. Schalkwijk

### Lidmaatschap

Voor lidmaatschap wende men zich tot de secretaris. Het lidmaatschap staat -behoudens ballotage- open voor academisch gegradueerden en hen, wier kennis of ervaring naar het oordeel van het bestuur een vruchtbaar lidmaatschap mogelijk maakt. De contributie bedraagt fl. 55,--.

Studenten aan universiteiten en hogescholen komen bij gevorderde studie in aanmerking voor een juniorlidmaatschap, waarbij 50% reductie wordt verleend op de contributie. Op aanvraag kan deze reductie ook aan anderen worden verleend.

### HET TIJDSCHRIFT

Het tijdschrift verschijnt zesmaal per jaar. Opgenomen worden artikelen op het gebied van de elektronica en van de telecommunicatie.

Auteurs die publicatie van hun wetenschappelijk werk in het tijdschrift wensen, wordt verzocht in een vroeg stadium kontakt op te nemen met de voorzitter van de redactie commissie.

De teksten moeten, getypt op door de redactie verstrekte tekstbladen, geheel persklaar voor de offsetdruk worden ingezonden.

Toestemming tot overnemen van artikelen of delen daarvan kan uitsluitend worden gegeven door de redactiecommissie. Alle rechten worden voorbehouden.

De abonnementsprijs van het tijdschrift bedraagt f 55,--. Aan leden wordt het tijdschrift kosteloos toegestuurd.

Tarieven en verdere inlichtingen over advertenties worden op aanvrage verstrekt door de voorzitter van de redactiecommissie.

### Redactiecommissie

Ir. M.Steffelaar, voorzitter

Ir. L.D.J. Eggermont

Ir. A. da Silva Curiel.

### DE EXAMENS

De examens door het Genootschap ingesteld en afgenomen zijn:

a. op lager technisch niveau: "Elektronica monteur NERG"

b. op middelbaar technisch niveau: Middelbaar Elektronica Technicus NERG"

Brochures waarin de exameneisen en het examenreglement zijn opgenomen kunnen schriftelijk worden aangevraagd bij de Administratie van de Examencommissie.

Voor deelname en inlichtingen wende men zich tot de Administratie van de Examencommissie NERG, Genemuidenstraat 279, den Haag, gironummer 6322 te den Haag.

### Examencommissie

Ir. J.H. Geels, voorzitter

Ing. A. de Jong, secretaris-penningmeester

### DEVICES FOR SIGNAL PROCESSING

Paul Jespers, Université Catholique de Louvain, Laboratoire de Microélectronique, Bâtiment Maxwell B - 1348 Louvain-la-Neuve - Belgium

### ABSTRACT

With the advent of LSI technology, signal processing hardware and software is slowly changing into dedicated IC's. A few examples are given in this paper, considering a TV-ghost cancellation circuit a portable reading wand and a speech processing system. Interesting is the fact that large systems which were totally unconceivable because uneconomical before the advent of LSI technology, now are being seriously considered for consumer and other applications.

### INTRODUCTION

Future telecommunication systems, data acquisition and transmission systems will draw heavily upon LSI and VLSI. It is quite obvious that microprocessors as well as dedicated IC's will share the job. The advent of high performance MOS compatible analog-digital circuits however, is an incentive to develop an ever increasing number of custom designed IC's. Hence devices for signal processing are emerging which are based on innovative designs using CCD's, transversal filters, recursive filters op amps, A/D and D/A converters, etc. Rather than trying to seize the phylosophy behind this evolution, some typical examples will be examined.

### TV GHOST CANCELLATION CIRCUIT

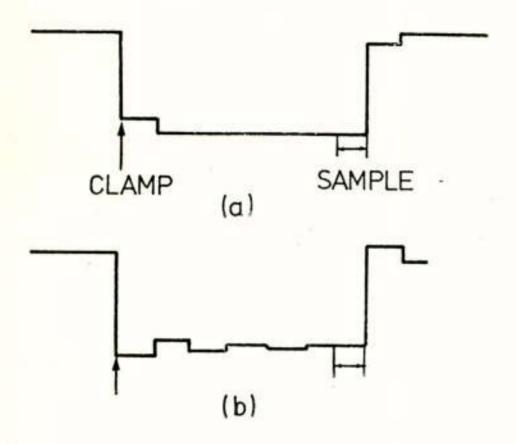

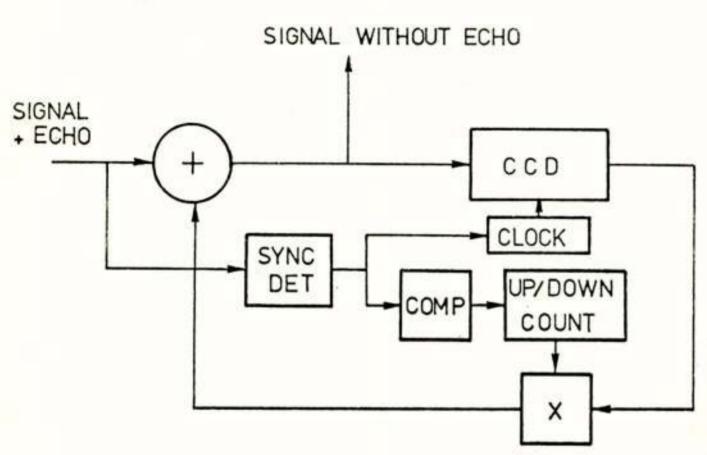

TV reception may be disturbed by spurious reflections which cause ghost images on the screen. The elimination of single undistorded echos may be achieved by means of an echo cancellation circuit which basically consists of a recursive CCD filter generating an artificial echo with the same delay and opposite polarity (1). The delay element for this application of course is a CCD line, clocked at an adjustable frequency. When properly time-set and with adequate amplitude of the delayed signal, exact cancellation of the unwanted echo can be achieved. A bloc diagram of the circuit is shown in fig. 1. Delay and gain adjustments of course must be set automatically. The TV synchronization signal during the field retrace period is used for this purpose as a test signal. Fig. 2a shows a single undistorded echo affecting the synchronization signal. Clamping the signal at the very beginning of the unit step and compairing it with the mean level of the unit step during the "sample" period, yields a measure of the echo's amplitude. The output signal of the comparator controls an up-down counter which provides a DC gain control signal to adjust the amplitude of the CCD output signal in order to equalize sample and clamp signals. It should be pointed out that before the correct amplitude adjustment is found, multiple reflexions appear which result from the recursivity of the filter (fig. 2b). This explains why the sample period is taken at the end of the sync. pulse.

Once the amplitude correctly set, the delay adjustment must be achieved. As long as overlapping of the echo versus the CCD signal occurs, or viceversa, a series of pulses is generated whose polarity referred to the echo determines without ambiguity whether the CCD delay should be lenghtened or shortened.

The same principle was also applied to 2-wire full-duplex data transmission systems (2).

### AUTOMATIC CHARACTER READING

In supermarkets, hospitals, libraries, reading wands can fulfil the need for fast and reliable data transcription from labels into other storage media, like magnetic tape or computer memory. Portability and cheapness are requirements which can be met satisfactorily by means of LSI implementation. Reading wands consist of a retina on which the image of a character is focused plus additional recognition circuitry. The retina may be a two dimensional CCD imager or a photodiode array (3). Single rows of photoelements are less attractive for the actual scanning speed of operators is unknown, unless mechanically probed. The recognition algorithm of course must be a simple one but it may be strongly dependent on the kind of material to be read. E.g. standard single font characters may well be recognized by means of a simple set of masks even when printing quality is not good. Multifont or handprinted characters however, may be recognized preferably on the basis of a topological analysis, thus are more demanding. An example of a feature extraction scheme is considered hereafter in which the recognition hardware consists of an LSI circuit with a microprocessor. The LSI circuit performs several repetitive preprocessing functions leaving the more refined feature extraction algorithms to the latter (4).

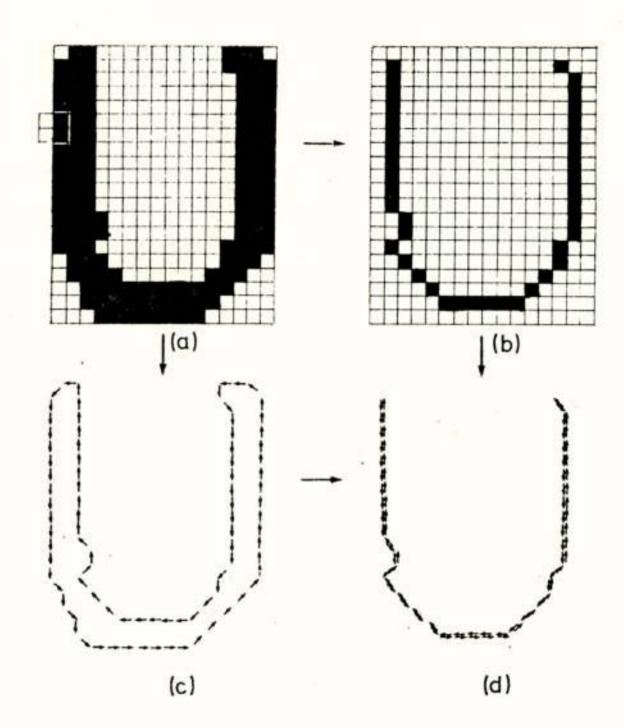

Binarisation of the image occurs when a full character is sensed by the retina. Isolated black dots and gaps in the tracing of the character first are removed by means of a separate IC (fill and delete). The subsequent image is stored in the memory of a contour analysis LSI where it is explored by means of a 2 x 2 squares contour detection window that searches for the character, locks onto the boundary and then is constrained to follow the edge of the pattern as described in fig. 3a. Decisions are taken concerning the tangent vector slope among eight quantized values multiple of  $\pi/4$ (5) and the subsequent window displacements in order to effectively track the boundary. The motion can be compared to the behaviour of a roller constrained to follow the character edge acting as a fixed cam. Context analysis is performed simultaneously. According to the value of the 12 squares surrounding the 2 x 2 contour detection window, black dots belonging to the character outer edge may be deleted or not.

Turning three or four time around the pattern provides complete character peeling (fig. 3c). The resulting string of 3 bit-coded vectors describing the contour of the skeletonized character (fig. 3d) is fed to the microprecessor for further analysis and feature extraction. These include branches and loops extraction, filtering, curvaturve determination, etc. leading to final classification of the character and the availability of its ASCII code at the system output.

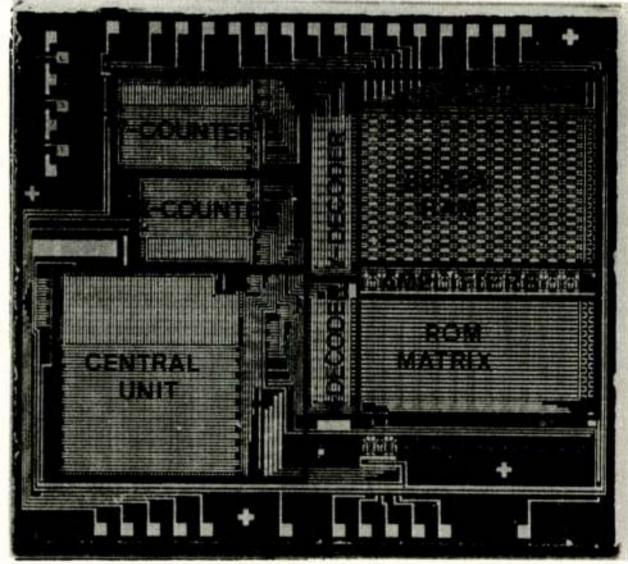

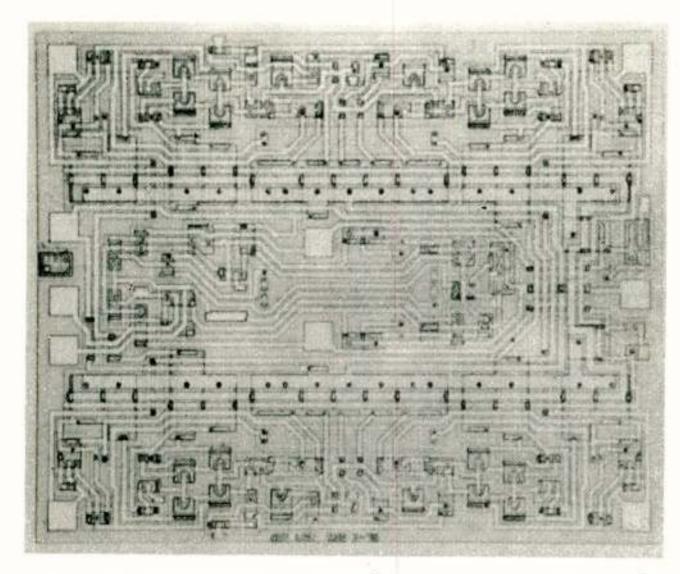

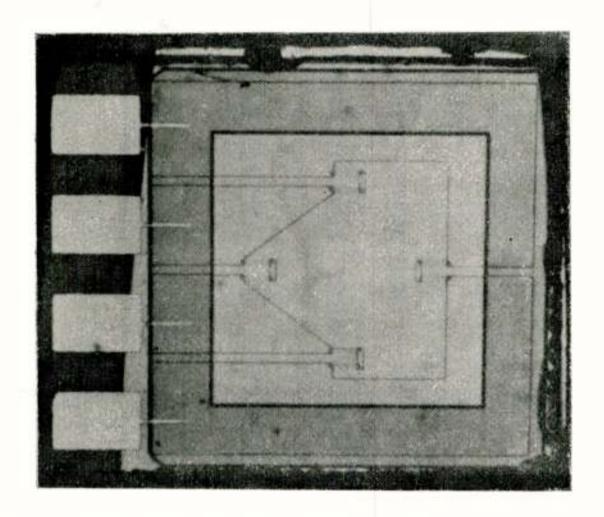

Fig. 4 shows the block diagram of the edge and skeleton detection MOS circuit. It consists of a  $32 \times 24$  dynamic one-transistor-per-cell RAM matrix. This memory is addressed accordingly to the actuel content of the previous  $2 \times 2$  contour detection window.

Four adjacent columns among the parallel outputs of the RAM amplifiers are selected by means of a ROM matrix in order to reconstitute the four 4-bit words necessary to check the values of the 2 x 2 window and its neighbourhood. These words feed the central unit which provides simultaneously a vector tangent to the boundary, incremental instructions for the X and Y counters, internal timing and the central unit decoder address and memory rewriting signal when a black dot must be deleted at the character periphery. The X and Y counter-decoder stages must accomodate to various incremental instructions like +2, +1, +0, -1. The skeletonization and linefollower random logic is easily implemented using a Programmable Logic Array (PLA). The versatility required from the counters makes PLA's more useful too for the scanning of the RAM matrix along both X and Y directions.

The experimental 3000-transistor circuit of fig.4 was fabricated using p-channel depletion load technology. Contour detection and thinning are performed in about 4msec leading to a global reading speed of 100 characters/sec. Continously deformed or handprinted characters are successfully recognized by the system with broad tolerances on the over-all sizes and thicknesses of the input patterns.

### VOCODERS

It is a well known fact that speech is a compressible source of information. Data rates as low as 50 to 70 bits/s have been measured when the speech signal was restricted to the textual context of utterances. We are interested however in auditory hints such as speaker's identity, etc. Hence, higher bit rates are required and most attempts to encode speech signals presently are based upon a min of 1000 bits/s.

Speech encoding furthermore, is raising a considerable amount of interest in view of PCM communications. Codecs already have been implemented successfully in I.C. form (6) and flow control procedures, such as packet switching, are becoming important research topics to help traffic decongestion. Similarly, the possibility to integrate channel Vocoders is seriously considered by I.C. manufacturers (7).

The channel Vocoder, invented by Homer Dudley in the 1930's, is a speech analysis system which is supposed to extract essential features from the speech signal such as :

- 1) is the signal quasi periodic (e.g. a vowel) or a voiceless sound (e.g. a "sh" or a "f") ?

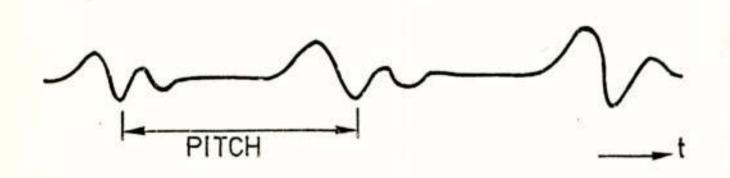

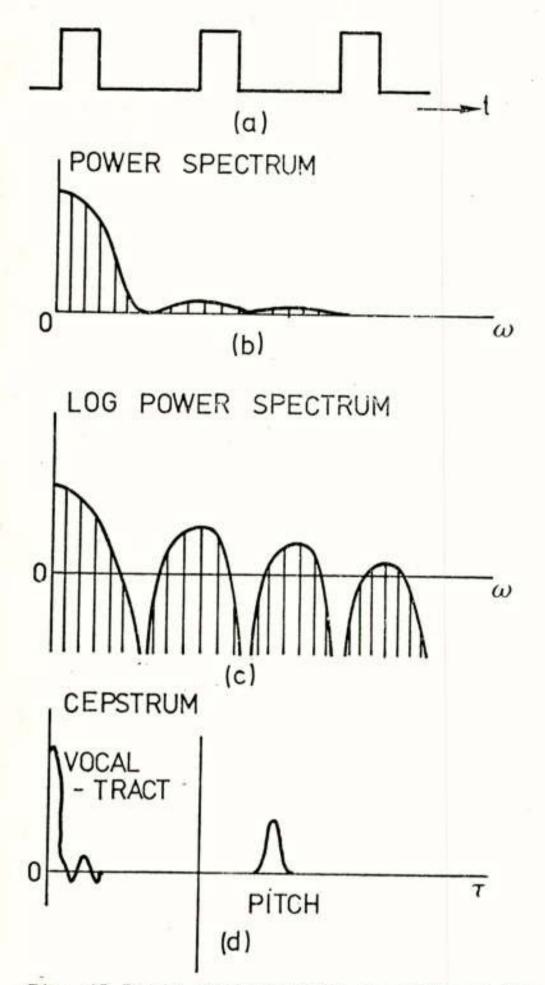

- 2) if the signal is periodic, estimate pitch and vocal-tract (fig. 5).

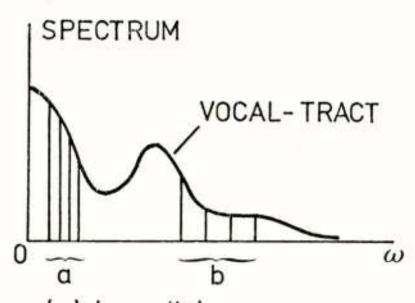

Voiceless sounds can be crudely parametized in terms of noise. Sustained vowels require spectral analysis tools to extract pitch and vocal-tract (fig. 6). In the Vocoder, a bank of narrowband filters is used in order to achieve spectral analysis. The actual bandwidths of the filters is the result of a compromise. If the bandwidths are very small (5 to 10 Hz) and if numerous filters are spaced very closely (e.g. 300 filters), a good spectral signature is obtained which yields both vocal-tract and pitch information. In the other case, when rather large bandwidths are considered (e.g. 100 Hz) a smooth spectrum is obtained that encompassed several harmonics and

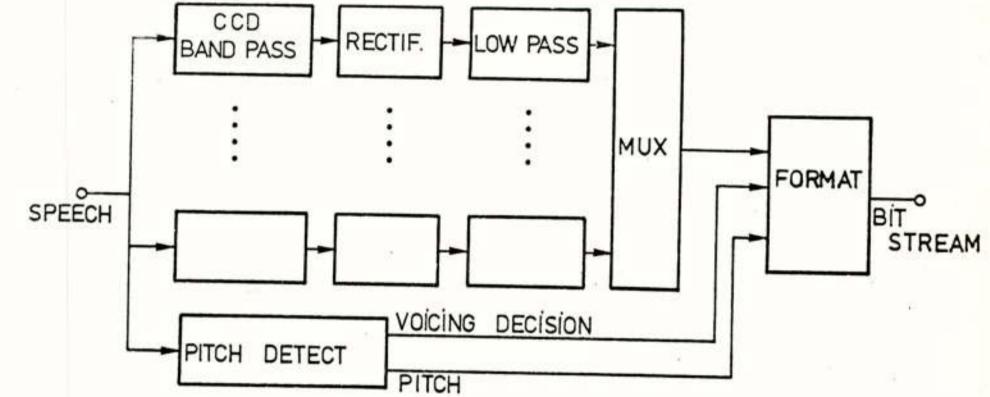

pitch information is lost. In the first case, a prohibitive number of filters and the difficulty to separate pitch and vocal-tract make this method useless for integration. In the second case, only a small number of filters is sufficient (e.g. 20 filters) but another algorithm must be looked at to recover pitch information. One is known as the Gold-Rabiner algorithm. It is a time domain method which consists to measure the time intervals between adjacent peaks and valleys of the speech waveform wherefrom the pitch is statistically estimated. A channel Vocoder based on this principle is illustrated in fig. 7 and its implantation on a single I.C. is under way. The circuit comprises 19 narrowband CCD transversal filters with bandwidths ranking from 120 Hz to 500 Hz. Their outputs are fully rectified and log sampled every 20 mS. This results in 39 bits vocal-tract information, to which 7 more bits must be added in order to restore pitch information, and 2 additional control bits for voiced-unvoiced decision, etc. The total bit stream (48 bits every 20 mS) amounts to 2.4 kbits/s.

Pitch tracking seems to be the most difficult circuit to integrate. Several different approaches

are being considered among which cepstrum evaluation perhaps may bring a satisfactorily answer.

The cepstrum heavily draws upon the existence of

Fast Fourier Transforms wich have already been

implemented in IC form (8). The basic idea behind

this can be understood from the following expression of the Fourier transform:

sion of the Fourier transform:

$$-j\frac{\mu t^{2}}{2} + \infty - j\frac{\mu t^{2}}{2} + j\frac{\mu t^{2}}{2}(p-t)^{2}$$

$$F(j\mu t) = e \qquad f(p)e \qquad e \qquad dp$$

$$premultiply \qquad postmultiply \qquad convolve$$

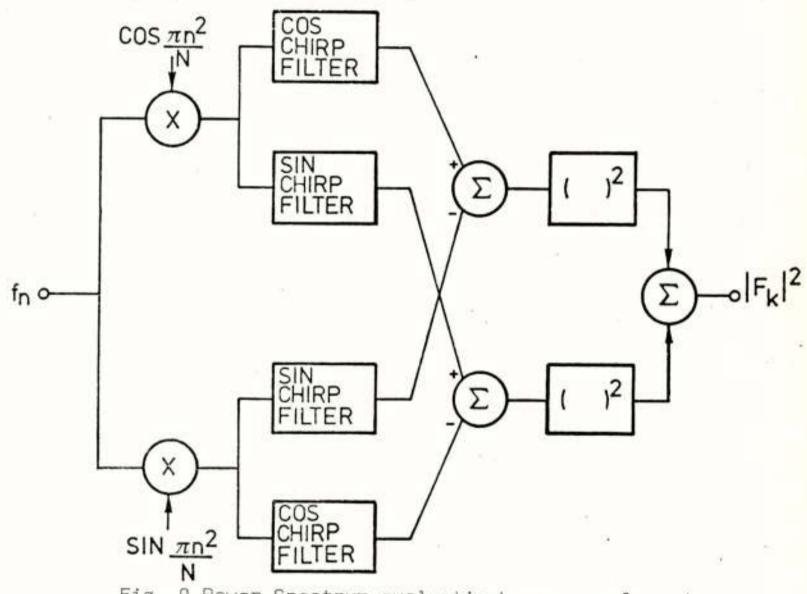

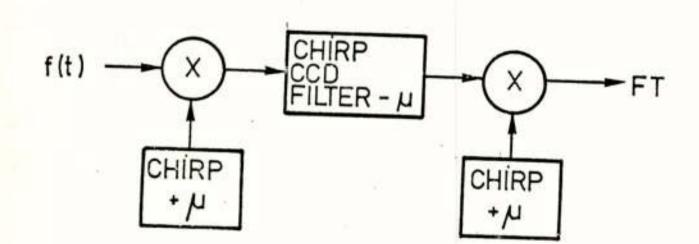

Exp (  $\pm$  j $\frac{\mu t^2}{2}$ ) in fact represents a vector of constant length rotating at a linearly varying speed. Consequently it does represent a linearly frequency modulated sine or cosine wave. The above expression can be viewed as shown in fig. 8. where premultiplication is achieved by means of a multiplying D to A converter (9), convolution is done by means of a chirp Z CCD transversal filter, and postmultiplication is similar to premultiplication. Notice that when the power spectrum only is required, postmultiplication may be omitted. Hence the circuit may be simplified as shown in fig. 9 representing the bloc diagram of an I.C. which is commercially available.

Let us now examine how pitch extraction effectively can be achieved by means of the Cepstrum which may be defined as (10).

C (t) =

$$|FT(\log|FT f(t)|^2)|^2$$

FT represents the Fourier Transform. Accordingly to this expression the cepstrum is the power spectrum of the log power spectrum of the speech signal. It may be considered as a cascade of two of the above IC's with a log transformation in between. Just to get some physical insight let us consider a simple example consisting of a periodic square wave (fig. 10a) whose power spectrum follows

the well known (sinwt²)/(wt)² law (fig. 10b). Taking the log of the power spectrum results in a modified spectral signature in which the importance of the smaller lobes has been emphasized relatively to the larger ones (fig. 10c). Considered as a time domain signal, the output signal of the chirp Z Fourier Transform circuit, resembles to the transient response of a band pass filter. Thus, after a second FT has been computed, we obtain a peak somewhere in the time domain (called quefrency) which is representative of the harmonics spacing of the first FT. Hence pitch detection and evaluation may be drawn from the cepstrum provided a window is used which eliminates the low quefrency components of the Ceptrum.

Another approach which perhaps is more powerful, is the computation of the complex cepstrum which is not subject to the loss of phase information like the power cepstrum. A slightly different approach is used here, since the computation of the complex cepstrum is based on a first FT, then a log conversion, then an inverse FT. At this point, pitch information again is available in the form of a sharp peak while the vocal-tract information is concentrated in the lower part of the cepstrum. Following this another FT of the windowed vocal-tract is used to obtain directly a smooth spectral signature.

Voice synthesis IC's must be used in order to restore the speech signal. Some applications however resume to the synthesis aspect only. This is the case for talking devices such as a talking calculator which is being developed for blind persons. In this application, the speech information is frozen in a ROM-like memory which is addressed accordingly to the spoken numbers. As IC consisting of a bank of variable size capacitors loaded to the same voltage and sequentially addressed has been developed for this purpose (11).

### CONCLUSION

The potentialities of LSI technology today and VLSI tomorrow enable system engineers to integrate sophisticated systems on a single chip, opening many new wide areas of applications. Not only an increasing number of existing systems is being implemented in IC's, but many new ones which were believed to be impractical for economical reasons, are slowly emerging accordingly to new consumer areas which have been identified. This situation is clearly evidenced in telecommunications where much signal processing hardware and software now is being implemented into devices for signal processing. Most interesting is the fact that these devices very often are based on entirely new algorithms which are not the obvious successors of the existing ones. In other words, the design of advanced dedicated IC's for signal processing perhaps is becoming a more challenging problem from the viewpoint of system design than from that of circuit design. IC systems engineers will need increasingly to be aware of the existence of many new interesting algorithms and, overal, they should be imaginative.

### REFERENCES

- (1) H.W. Hanneman and B. Visser. An experimental TV ghost cancellation circuit with automatic gain control. CCD conference record, 1976 Edimburgh.

- (2) H.C. Van den Elzen, P.J. van Gerwen, W.A.M. Snijders.

Echo cancellation in a 2-wire full-duplex data transmission system with bipolar encoding. NTC conference 1976, Dallas, Texas.

- (3) P.Jespers, F.Van de Wiele, M.H.White. Solid State Imaging Noordnoff Int. Publishing, Leyden Series E: Applied Science, n° 16.

- (4) M.Rahier, P.Jespers.

A low-cost hand-carried OCR system implemented with monolithic IC's.

The 4th International Joint Conference on Pattern Recognition Nov. 7-10, 1978, Kyoto Japon.

- (5) H.Freeman.

On the encoding of arbitrary geometric configuration.

IRE Trans on Electronic Computers, June 1961.

- (6) J.Compeers, H.De Man.

Nonuniform pulse code modulation encoder using double polysilicon technology.

IEEE Journal of Solid State, specialissue on ESSCIRC 1977, June 1978.

- (7) B.Gold.

Digital Speech Networks.

Proc. of IEEE, vol. 65, n° 12, Dec. 1977.

- (8) D.D.Buss, R.W.Brodensen, C.R.Hewes. Charge coupled devices for Analog Signal Processing. Proc. of IEEE, vol. 64, n° 5, May 1976.

- (9) J.F. Albarran D.Hodges.

A charge transfer multiplying digital-to-analog converter.

IEEE Intern. Solid State Circuit Conference Digest of Technical Papers 1976.

p. 202-203.

- (10) M.A.Jack, P.M.Grant, J.H.Collins. .

Waveform detection and classification with SAW

Cepstrum Analysis.

IEEE Trans on Aerospace and Electronic Systems.

Vol. AES-13, n° 6, nov. 1977.

and A.M.Noll.

Short-time Spectrum and Cepstrum Techniques for Vocal-pitch detection.

Journal of Acoustical Soc. of America, vol 36, n° 2, febr. 1964.

(11) E.Bruun, Ole Olesen.

Analog Capacitance ROM with IGFET Bucket-Brigade

Schift Register.

IEEE Journal of Solid State Circuits, vol. SC 10,

n° 1, febr. 1975.

Fig. 1

- a) Use of sync. signal during the field retrace period in order to adjust amplitude and delay of the echo cancellation circuit.

- b) When improperly set, the CCD recursive filter generates a series of unwanted echos.

Fig. 2

Bloc-diagram of the echo-cancellation circuit.

Fig. 5 Voice signal.

Fig. 3

- a) Binary image of a U

- b) Peeled character

- c) String of tangent vectors before peeling

- d) String of tangent vectors after peeling.

Fig. 4 Microphotograph of contour following circuit.

Fig. 10 Pitch determination by means of the Cepstrum

- a) Periodic square wave

- b) Power Spectrum

- c) Log. power Spectrum

- d) Cepstrum

(a) low pitch

Fig. 6

voiced signal.

Short time Spectrum of

Fig. 9 Power Spectrum evaluation by means of quad chirped transversal filter.

Fig. 7 Bloc-diagram of a Vocoder.

Fig. 8 The chirp Z Fourier Transform.

J.O. Voorman

### Abstract

Gyrator principles - definition, electronic design and controllability - are explained. Filter applications as well as oscillator applications (ending up with the PAGYR IC) are surveyed with reference to the various gyrator properties exploited.

### Introduction

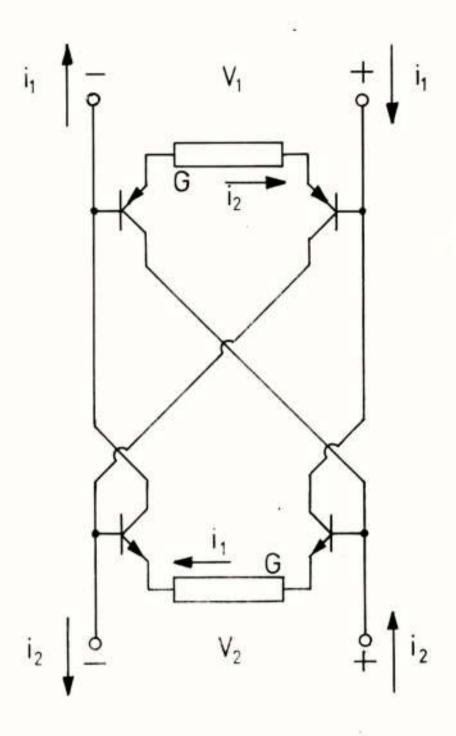

In 1948 Tellegen presented his famous paper: "The Gyrator, a new electric network element" [1]. He introduced the gyrator as a passive electric two-port with equations

$$i_1 = +Gv_2,$$

$i_2 = -Gv_1,$

(1)

where G is the gyration conductance. The opposite signs in the two equations indicated something new: the gyrator is non-reciprocal.

The best-known passive implementations (in microwave isolators and circulators) were based on the Hall effect and on the Faraday effect. For low frequencies the artificial inductance of a capacitively loaded gyrator is an attractive proposition for simulating bulky and expensive coils. A satisfactory implementation was not found, however, until active parts were used for the gyrator construction. The first to be introduced was a triode gyrator (Wheeler 1948, Klein 1952), followed by a pentode gyrator (Sharpe 1957) and a first transistor gyrator (Ghausi and McCarthy 1963). It is due particularly to the rapid development of integrated circuits that practical gyrators have become feasible devices.

### Construction principle of an electronic gyrator

A straightforward implementation of the gyrator equations (as two voltage-controlled current sources) is shown in fig. 1. The accuracy requirements, comparable to those for coils, necessitate the use of composite (artificial) transistors where a single transistor is drawn in fig. 1. Supply current circuitry completes the gyrator. An integrated version (TCA 580) is on the market [2, 3].

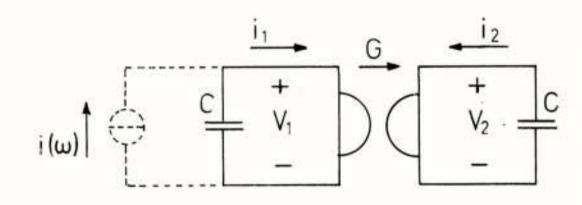

# Signal amplitude detection on a gyrator-capacitor resonant circuit

Let us consider a "symmetric" resonant circuit (constituted by a gyrator with a capacitor connected across its secondary port, thus forming together an inductance, shunted by another capacitor of the same value). We apply a signal current of variable frequency (fig. 2).

Voltage  $v_1$  shows a resonance character. The resonant frequency is

$$\omega_{O} = \frac{1}{\sqrt{LC}} = \frac{G}{C}.$$

(2)

So far there is nothing unusual.

However, unlike in the case of an LC resonant circuit, we can measure a second voltage (v2), which shows a similar resonance character. If

The author is with Philips Research Laboratories, Eindhoven, the Netherlands.

Fig. 1. Principle of the construction of an electronic gyrator from two voltage-controlled current sources (i<sub>1</sub> = +Gv<sub>2</sub>, i<sub>2</sub> = -Gv<sub>1</sub>).

Fig. 2. A "symmetric" gyrator-capacitor resonance circuit.

$$v_1 = a \cos \omega t$$

, (3)

then

$$v_2 \approx a \sin \omega t$$

. (4)

The two voltages have equal amplitudes and a 90° phase difference. The electric charge is "toggling" between the two capacitors.

A similar relationship is found for the signal currents  $(i_1 \approx b \text{ sin}\omega t, i_2 \approx -b \text{ cos}\omega t)$ . Therefore,  $(i_1^2 + i_2^2)^{\frac{1}{2}} = b$  (5)

is a yardstick for the signal current in the gyrator.

The above property can be used essentially in two ways:

in <u>filter applications</u> to control the supply current in the gyrator (in proportion to the signal level), thus saving mean supply power, and

the amplitude b can be stabilized to some reference value b<sub>0</sub> (if b > b<sub>0</sub> the resonant circuit is damped, if b < b<sub>0</sub> it is undamped) and an oscillator is obtained.

### Filter applications

The first aim in designing electronic gyrators was

to simulate inductance. Particularly important in this application is the <u>losslessness</u> of the gyrator [4].

In other applications the non-reciprocity, or better the anti-reciprocity, plays a crucial role, for instance in quadrature filters. An example is a matched-filter receiver for FSK signals [5].

Variable gyrators (i.e. gyrators with a variable gyration conductance) can be employed in variable filters. From the basic gyrator construction in fig. 1 it is seen that two conductances have to be varied together. The above can be obtained with current multiplication based on the exponential characteristic of bipolar transistors [6].

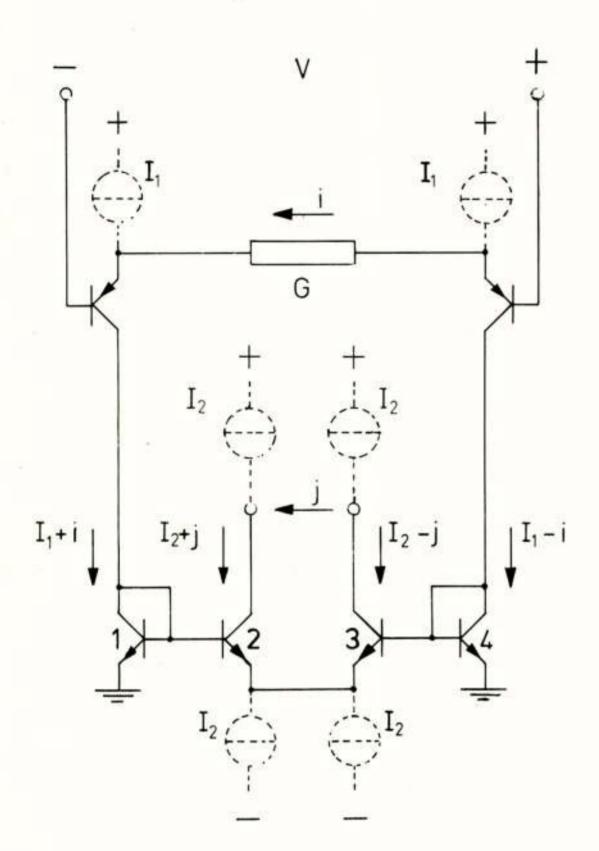

Fig. 3. Variable transconductance principle. Input voltage v causes a current i in conductance G. For the matched transistors 1, 2, 3 and 4: VBE1 - VBE2 + VBE3 - VBE4 = 0 and hence IC1IC3 = IC2IC4 or Ij = I2i. The transconductance j/v is GI2/I1, from which the ratio of the supply currents I2/I1 can be varied.

In fig. 3 the principle of a variable voltagecontrolled current source is shown. Its transconductance is given by

$$\frac{\mathbf{j}}{\mathbf{v}} = \mathbf{G} \, \frac{\mathbf{I}_2}{\mathbf{I}_1} \, . \tag{6}$$

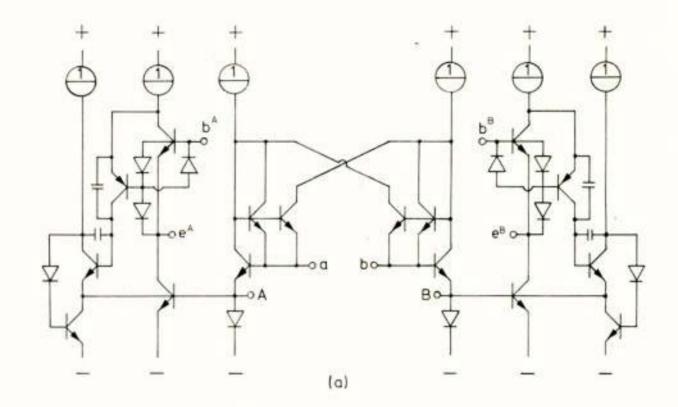

Two stages in anti-parallel (fig. 1) form a variable gyrator. The supply current ratio  $I_2/I_1$  controls the gyration conductance. An accurate design, free from latch-up and stable with overflow, is shown in figures 4a and 4b.

### Adaptive gyrator

An adaptive gyrator is variable and has squarers for signal amplitude detection (eq. 5). A squarer

Fig. 4. Adaptive gyrator stage.

An input voltage v (between b^A and b^B) causes a current i in a conductance G (to be connected between e^A and e^B). The output current iI2/I1 (compare with fig. 3) is taken from c^A and c^B. In fig. c a squarer (see eq. 5) is shown. Two of these stages connected in anti-parallel form an adaptive gyrator.

is shown in fig. 4c. Its output current is given by

$$i_p - i_q = 2 \frac{i^2}{I_1}$$

, (7)

where i is the signal current induced in the gyration conductance G (to be connected between  $e^{A}$  and  $e^{B}$ ).

The adaptive gyrator chip (fig. 5) contains integrated gyration conductances. The supply current ratio  $I_2/I_1$  is derived from the ratio of an external conductance  $G_e$  and a likewise integrated conductance  $G_i$ . Thus, the effective gyration conductance

$$G_{\text{eff}} = \frac{G}{G_i} G_{\text{e}}$$

(8)

contains the accurate (fixed) ratio G/Gi of matched monolithic conductances.

### Gyrator oscillator

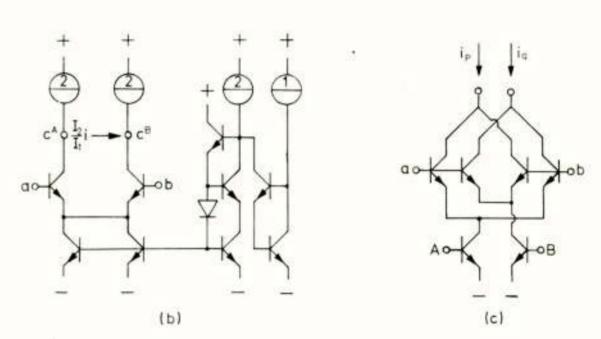

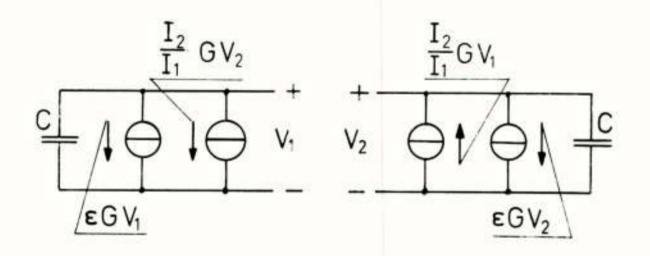

The detection of the amplitude b of the signal current in the gryator is described in eq. 5. A principle of amplitude stabilization is illustrated in fig. 6. Two controlled signal current sources damp or undamp the circuit, depending on the sign of  $\varepsilon$ .

The descriptive equations are

$$C\frac{dv_1}{dt} + \varepsilon Gv_1 + \frac{I_2}{I_1}Gv_2 = 0,$$

$$C\frac{dv_2}{dt} + \varepsilon Gv_2 - \frac{I_2}{I_1}Gv_1 = 0.$$

(9)

Fig. 5. Experimental adaptive gyrator chip (2x3 mm<sup>2</sup>). Its gyration conductance is controlled by a single external resistor. The signal amplitude detection can be used either for supply current control (in filters) or for signal amplitude stabilization (oscillators).

Fig. 6. Gyrator oscillator arrangement. The centre two voltage-controlled current sources form a variable gyrator. The outer two provide for the damping or undamping, depending on the sign of ε.

Inserting

$$v_1 = a \cos\phi(t),$$

$$v_2 = a \sin\phi(t),$$

(10)

the variables can be separated (which is not possible in the case of a Van der Pol oscillator) [7]. The result is

$$\frac{da}{dt} + \varepsilon \frac{G}{C}a = 0, \qquad (11)$$

$$\frac{d\phi}{dt} = \frac{G}{C} \frac{I_2}{I_1} . \tag{12}$$

The oscillator gives two output signals in quadrature (eq. 10). The amplitude is stabilized at a value  $a_0$ , where  $\varepsilon(a_0)=0$  and  $(a-a_0)\varepsilon(a)>0$  for  $a\neq a_0$  (eq. 11). The instantaneous frequency of the signal is directly controlled by the value of  $I_2$  (eq. 12). The arrangement is an ideal frequency modulator [8].

### Gyrator oscillator applications

The gyrator oscillator is ideally suited for low frequency FM, PM and FSK transmitters.

An example is an FSK transmitter. Its bandpass filter can be avoided by applying a combination of trapezoidal frequency modulation and some percents of amplitude modulation [5].

In phase and frequency locked loops the clean sinewave (no locking on harmonics and subharmonics) and the availability of the quadrature signal can be of advantage. An example of the above is the PAGYR.

### PAGYR

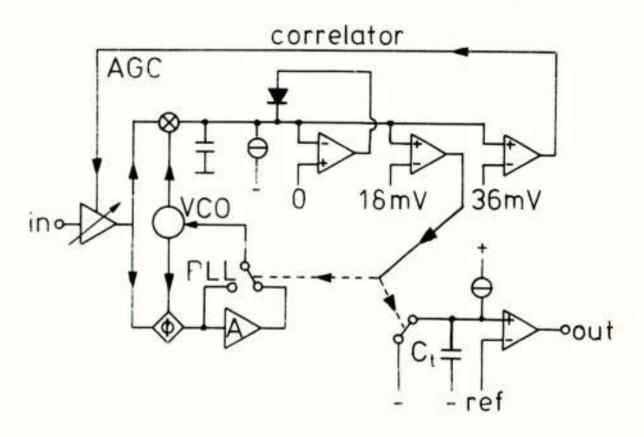

The PAger GYRator circuit [9] is the selective part of a tone encoder/decoder intended for use in selective calling in mobile radio. Call codes are dealt with on a digit by digit (tone by tone) basis.

Fig. 7. Block diagram of the PAGYR.

The block diagram of the PAGYR (fig. 7) shows a gyrator Voltage-Controlled Oscillator (VCO) with two quadrature outputs in a Phase-Locked Loop (PLL). The oscillator is switched from frequency to frequency by switching a resistor array. The correlator detects whether there is an input signal or not and it controls the switching of the loop gain of the VCO (for fast acquisition). If a tone is found present during a certain time the output goes "high". The switching from tone to tone, from encoding to decoding, relaying etc. is controlled by a second integrated circuit.

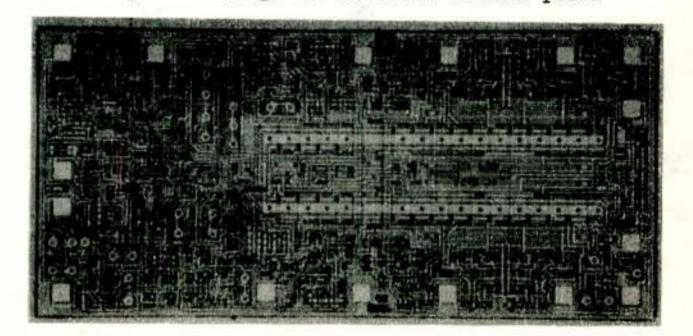

The PAGYR is integrated in a standard bipolar process. The chip size is 2x4.2 mm<sup>2</sup>. It contains 360 components (fig. 8). Relevant circuit parts

Fig. 8. PAGYR chip. The gyrator oscillator is in the right hand part. The circuit is integrated in a standard bipolar process and measures 2x4.2 mm<sup>2</sup>.

are compensated for base current and Early effect. Component positioning on the chip is such that linear gradients in transistor and resistor properties have no influence on the circuit behaviour. Some further data are

supply voltage: 3 - 10 V,

power consumption: 1 mW (3V),

frequency range: 50 - 5000 Hz,

(linearly controlled)

capture range (2 - 20 %),

(either proportional to or independent of oscillator frequency)

AGC range: 40 dB.

### Conclusion

A survey of the properties and applications of adaptive gyrators reveals their attractiveness as new components for integrated selectivity. Filter applications (inductance simulation, quadrature filters, variable filters) and oscillator applications (ideal frequency modulator, FSK transmitter, PAGYR) are distinguished. The PAGYR IC proves the feasibility in production.

### References

(1) B.D.H. Tellegen (1948)

"The Gyrator, a new electric network element"

Philips Res. Reports 3, 81-101.

(2) J.O. Voorman and A. Biesheuvel (1972)

"An electronic gyrator"

IEEE J. of Solid-State Circuits SC-7, 469-474.

(3) Philips, Electronic Components and Materials

- Data handbook (1976)

Semiconductors and Integrated Circuits

Professional analogue IC's

- "The TCA 580 integrated gyrator" Electronic applications bulletin 34 (1977) 109-122, 148-161.

(4) H.J. Orchard (1966)

"Inductorless filters"

Electronics Letters 2, 224-225.

(5) J.O. Voorman (1977)

"The gyrator as a monolithic circuit in electronic systems"

Thesis, University of Nijmegen.

(6) B. Gilbert (1968)

"A new wide-band amplifier technique"

IEEE J. of Solid-State Circuits SC-3, 353-365.

(7) N. Minorsky (1947)

"Introduction to non-linear mechanics"

Ann Arbor, Edwards.

(8) J.O. Voorman (1974)

"Ideal frequency modulator"

Electronics Letters 10, 387-388.

(9) J.O. Voorman and A. Wijker (1978)

"PAGYR, a new component for selective calling"

Philips Telecommunication Review 36, 31-40.

REVIEW OF THE EVOLUTION OF TELETEXT AND VIEWDATA.

Gerald Offley Crowther

### Introduction

The words Teletext and Viewdata have created a major impact on the electronics industry involving most of the major branches: Broadcasting, Telecommunications, the Television and Data Handling industries. The detailed interests of each individual industry are clearly different and there is now a danger that the initial benefits, low cost standard communication systems, may be lost in the conflict of different aims.

It is perhaps useful to review the aims and reasons which led to the adoption of the present U.K. Teletext and Viewdata systems.

The two systems have always been regarded as complementary. Teletext provides a natural method of providing rapidly changing information to many users. Viewdata, on the other hand, supplies individual data from a wide data base. As a consequence, it has been regarded as fundamental that the two systems should be economically compatible.

The prime aim for both systems has been to bring data handling systems into the home as part of the domestic colour T.V. set, thus creating a new and potentially large market. It was recognised from the outset that the two systems would also be of great interest to the professional areas (specifically Viewdata) where the final requirements may be significantly different to those of the domestic market.

In the design specifications of both systems considerable attention has been paid to minimising the additional cost onto the domestic colour T.V. set in the initial stages. At the same time redundancy has been incorporated to allow significant enhancement of the user facilities as advances in semiconductor technology permit and the needs arise without imposing cost penalties on the basic decoder. The above feature has been achieved in such a way that the present LSI decoder systems will continue to function correctly by rejecting signals intended for more enhanced decoders.

A number of doubts and uncertainties have been expressed as to the suitability of the present U.K. specifications for Europe, U.S.A. and other locations.

The comments centre around four main topics:-

- 1. The data rate of Teletext,

- The fixed relationship between transmitted data on a T.V. line and the displayed row of Teletext,

- The extension for European and non-Latin languages (both systems),

- 4. The display control facilities (both systems).

- 2. Choice of Data Bit Rate in Teletext

The choice of data bit rate is a compromise between the bandwidth of the system and the desire to maximise the data transmitted within the given bandwidth.

The present data clock rate of 6.9375MHz was based on an extensive field trial on System I (1 & 2) in the U.K. and System B (3) with data clock rates ranging from 4.5MHz to the present 6.935MHz. The error rates over the whole range were insignificantly different.

Subsequent experience in the U.K. has proved the choice to be the correct one and this is being confirmed in some European countries.

Significant problems have, however, arisen in countries with mountainous regions due to short echoes insufficient to disturb the T.V. picture. It has been shown by RAI in Italy (4) that a significant improvement can be achieved by the use of biphase bit coding rather than the present NRZ system but at the severe penalty of halving the data rate for the same data clock rate. The improvement is associated with the better clock synchronisation and smaller bandwidth of the data signal.

- A judgement has now to be made whether to:-

- adopt the biphase system and accept the reduction in data rate by a factor of two,

- adopt biphase system only where the terrain forces its adoption,

- 3. improve the present NRZ receiver decoders to cope with the large echoes.

Option 3 has major attractions since the main user criticism of Teletext is the waiting time.

It would also appear that the margin of improvement required could be achieved by the natural advances in T.V. set design resulting from LSI technologies coupled with improvements in the transmission system (particularly the introduction of data regenerators).

The features made possible by LSI technology are accurate digital tuning, surface wave i.f. filters, synchronous detection and, in the future, echo cancellation.

The major improvement will undoubtedly come in better techniques for data recovery in the Teletext decoder. The present decoders employing peak to peak detection are particularly susceptible to echoes. There is good reason to believe that better techniques will be available in the foreseeable future.

Option 2 is a possible solution and LSI receiver decoders could be designed to automatically switch to the appropriate system with minimum on costs.

In conclusion, it must be stated that neither solution is suitable for NTSC systems. Compatible systems can be designed readily which permit the use of the present LSI decoders with minor modifications. This can be achieved either by reducing the clock rate by a factor of two and only transmit half a row of data per T.V. line or by reducing the number of characters displayed per row from 40 to 32 and, therefore, reduce the clock rate. The former solution is to be preferred as it gives more optimal display format.

# The Direct Relationship Between The Data Inserted on a T.V. Line and a Displayed Data Row in Teletext

At the outset it has to be recognised that Teletext, unlike Viewdata, is a non-interactive system. The transmission and decoder concepts have to be designed to give the user the appearance of an interactive system.

There are two instances where the fixed relationship between the transmitted data and display data on a T.V. line is of importance. The first when the user requests a new page and, secondly, when errors occur in the transmission.

To cover the first aspect all present LSI decoders display on screen every page header. Since the page number is always transmitted in the same location it will appear on screen as a continually changing or rolling display. It has been arranged that the page number rolls from the instant the new page is requested until its acquisition. The user is given immediate feedback, the system is functioning correctly even though the page requested is not being transmitted. Other variants on the facility are clearly possible but they can only be achieved economically if the one-to-one relationship exists.

More important, is to examine the effects of errors If errors occur either in a transmission. detected or undetected, the only possible action is to wait for a repeat transmission. Furthermore, since errors are likely to be caused by noise, probably aided by other distortion phenomena (reflections, asymetric distortions in equipment and co-channel interference); it is probable that the next reception of the required text will contain errors in new locations. Advantage can be taken of this fact if the coding system is well It can be arranged that an integration of correct text automatically takes place by the use of simple parity checks over two or three recep-For this to be tions of the wanted data. achieved it is vital that the page selection and the page formatting information is protected against disturbance. Hamming codes for the protection and correction of the address data are employed.

At first sight it would appear that the integration can be achieved without the strict relationship with considerable advantage in the display facilities.

In a non-synchronous system the presence of page formatting information has to be marked by a flag. The flag to be recognised has to be of the same form as the data and is, therefore, just as corruptible. If the flag is missed for any reason, the decoder must interpret the following information as data which could be the start of an unrelated page. Thus, rather than obtaining the desired integration of correct data, the reverse may well occur.

In the U.K. synchronous system the page formatting data always occurs at the start of a T.V. line and, in essence, the line sync pulses act as the flag. The normal flywheel techniques give complete protection to this method of flagging.

In conclusion, it is worth mentioning that conventional methods of protecting serial data such as BCC or CRC are not as effective as the combination of parity and Hamming protection.

### 4. Other Languages

It is recognised that the present Viewdata and Teletext proposals do not cater for the European and non-Latin languages. There is, however, redundancy in both systems to cater economically for both these requirements.

In both the systems the primary display medium is a conventionally scanned picture tube. This dictates that all characters have to be stored within the decoder character generator in the form in which they will ultimately be displayed.

To minimise the cost of the decoder it is essential to avoid code changing within the decoder and it is, therefore, necessary to transmit a simple seven bit code representing every character displayed. The use of the National usage codes of ISO646 can be exploited to achieve these aims. Normally, within a country a single language will be employed and each page may then be prefaced by a code representing the character set or language to be employed. The advantage of the proposal is that it simplifies the transmission by avoiding 'escape' sequences and retains the one to one relationship discussed earlier for Teletext.

In Viewdata the proposal is readily implemented by a single three character 'escape' sequence as defined in ISO2022.

For Teletext, use is made of spare codes built into the present specification. These include three control bits (C12, C13 and C14) and Rows 24 to 31 which present decoders must reject. It is permissible to raise one or more of these spare rows to the status of a page header or Row O with additional control bits with special meaning. One combination, for instance, would define the character set to be employed. A typical multilanguage transmission would then be as follows:-

| Row | 0  | Page n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                              |

|-----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Row | 1  | Character data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                              |

|     |    | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page n recognised by                         |

|     |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | present and future                           |

|     |    | 7 WT 1997                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | decoders (normal                             |

| Row | 23 | Character data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | character set)                               |

| Row | 0  | Page 15 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                              |

| Row | 31 | Page m language x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                              |

| Row | 1  | Character data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                              |

| •   |    | on made to the arrespondent of the description of the second of the seco | Page m and (m + 1)                           |

|     |    | 85 <b>4</b> 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | recognised by future                         |

|     |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | decoders only                                |

| Row | 23 | Character data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10-3 (10-15) (10-15) (10-15) (10-15) (10-15) |

| Row | 31 | Page (m + 1)<br>language z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                              |

| etc | •  | March 6 - 10593 - 596 11797                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                              |

Existing decoders must not receive data initiated by the secondary page header (Row 31). Thus, Row O Page 15 15 is used as a terminator. This is a page which cannot be selected on any decoder but can be transmitted, and in common with all row O's terminates the previous page. The page code 15 15 has already been used for this purpose in the U.K.

The techniques described above can be readily extended to give several languages on a single displayed page.

Before a scheme, as described above, can be imple-

mented, an agreement will have to be reached on how many additional characters will be permanently stored in ROM in the decoder character generator. It would be unreasonable to expect every symbol likely to be required to be permanently stored in every decoder. To cover the situation it has been proposed by the BBC (5) that the first part of the transmission should contain 10 X 6 dot pattern for a new character set which would be stored in a RAM but employed as a ROM within the decoder character The techniques described above would generator. enable the transmission of a full 96 character set in both Viewdata and Teletext. Furthermore, the proposal is a logical extension to the concept of the National usage codes.

To conclude, it is worth pointing out that the above technique can be employed to achieve enhanced graphics by joining together adjacent character blocks to form a single large block.

### 5. The Display Control Facilities

The display control facilities (colour of alphanumerics, flash, etc.) in the present systems are transmitted and stored in the decoder as part of the text. On the display these control characters are normally displayed as spaces. In most pages of text this is not a severe limitation, but it can be undesirable in certain displays employing the graphics capabilities of the system. The objectionable black space between a colour change can be avoided by employing the 'graphics hold' facility. In this case, the previously displayed graphics symbol is repeated in shape and colour at the location of the control character.

It has been proposed that a further enhancement of the system could be achieved if all the control characters could apply instantaneously to all display locations. The consequence of the proposal is that the memory size and, therefore, the cost of the decoder increases significantly but also the synchronous system for Teletext can no longer be employed. The proposal could, however, be implemented in Viewdata as an enhancement using the two character 'escape' sequences.

Before implementing parallel control characters, it is worth asking whether the necessary substantial and inefficiently employed memory could not be better employed for other features. As an example, a multipage memory would be of great benefit in both Viewdata and Teletext but would be prohibitively expensive with parallel display coding.

### 6. Conclusion

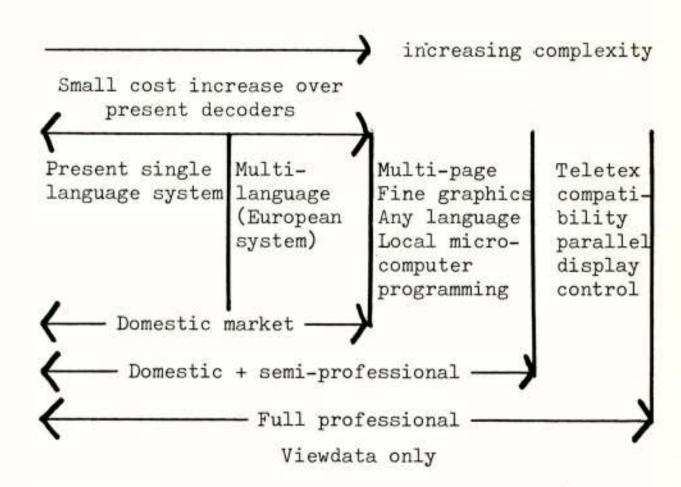

It has been demonstrated how the present U.K. systems can be enhanced to meet European and World requirements. It can be achieved with a minimum cost in the decoders and retaining the robustness of the present Teletext transmissions. The following table summarises the potential of the present Teletext and Viewdata.

The system has been designed for upwards compatibility.

The author is with Mullard Application Laboratory, Mullard Limited, London, England.

### References

- (1). "Ceefax: Uhf Field Trials", By D.W. Stebbings, B.B.C. Research, April 1975.

- (2). "An Assessment of Teletext Data Transmission over the Uhf Television Network", By L.A. Sherry, Teletext Transmission Working Group Note 10, I.B.A.

- (3). "Teletext Field Tests in Bavaria April 16th to 24th 1975", August 1976, Published By the B.B.C., I.B.A. and I.R.T.

- (4). "Technical Problems For Introduction In Italy Of A "Teletext" Service", By M. Cominetti, P. D'Amato, R.A.I., Turin, Italy.

- (5). "Alphabets for Ceefax", B.B.C. Engineering, December 1977.

### K. Mouthaan

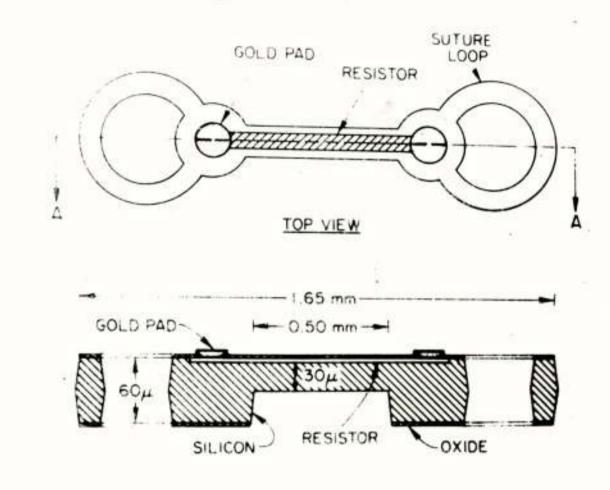

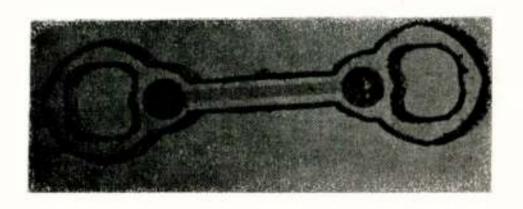

### Introduction